Riak kuasa pensuisan tidak dapat dielakkan. Tujuan utama kami adalah untuk mengurangkan riak keluaran ke tahap yang boleh diterima. Penyelesaian paling asas untuk mencapai tujuan ini adalah untuk mengelakkan penjanaan riak. Pertama sekali Dan punca.

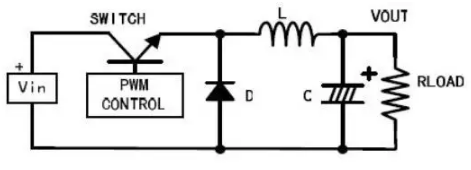

Dengan suis SWITCH, arus dalam kearuhan L juga turun naik ke atas dan ke bawah pada nilai sah arus keluaran. Oleh itu, akan ada juga riak yang sama frekuensinya dengan Suis pada hujung output. Secara amnya, riak riber merujuk kepada ini, yang berkaitan dengan kapasiti kapasitor keluaran dan ESR. Kekerapan riak ini adalah sama dengan bekalan kuasa pensuisan, dengan julat puluhan hingga ratusan kHz.

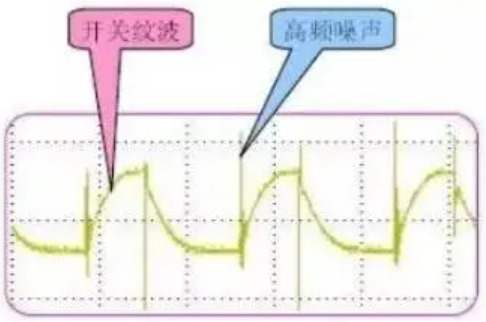

Di samping itu, Suis biasanya menggunakan transistor bipolar atau MOSFET. Tidak kira yang mana satu, akan ada masa naik dan turun apabila ia dihidupkan dan mati. Pada masa ini, tiada bunyi bising dalam litar yang sama dengan masa pertambahan seperti masa penurunan kenaikan Suis, atau beberapa kali, dan biasanya berpuluh-puluh MHz. Begitu juga, diod D berada dalam pemulihan terbalik. Litar setara ialah siri kapasitor rintangan dan induktor, yang akan menyebabkan resonans, dan frekuensi hingar ialah berpuluh-puluh MHz. Kedua-dua bunyi ini biasanya dipanggil hingar frekuensi tinggi, dan amplitud biasanya lebih besar daripada riak.

Jika ia adalah penukar AC / DC, selain dua riak (noise) di atas, terdapat juga bunyi AC. Kekerapan ialah kekerapan bekalan kuasa AC input, kira-kira 50-60Hz. Terdapat juga bunyi mod bersama, kerana peranti kuasa banyak bekalan kuasa pensuisan menggunakan cangkerang sebagai radiator, yang menghasilkan kapasitans yang setara.

Pengukuran riak kuasa pensuisan

Keperluan asas:

Gandingan dengan osiloskop AC

Had lebar jalur 20MHz

Cabut palam wayar pembumian probe

1.Gandingan AC adalah untuk mengeluarkan voltan DC superposisi dan mendapatkan bentuk gelombang yang tepat.

2. Membuka had lebar jalur 20MHz adalah untuk mengelakkan gangguan bunyi frekuensi tinggi dan mengelakkan ralat. Oleh kerana amplitud komposisi frekuensi tinggi adalah besar, ia harus dikeluarkan apabila diukur.

3. Cabut palam klip tanah probe osiloskop, dan gunakan ukuran ukuran tanah untuk mengurangkan gangguan. Banyak jabatan tidak mempunyai cincin tanah. Tetapi pertimbangkan faktor ini apabila menilai sama ada ia layak.

Perkara lain ialah menggunakan terminal 50Ω. Mengikut maklumat osiloskop, modul 50Ω adalah untuk mengeluarkan komponen DC dan mengukur komponen AC dengan tepat. Walau bagaimanapun, terdapat beberapa osiloskop dengan probe khas sedemikian. Dalam kebanyakan kes, penggunaan probe dari 100kΩ hingga 10MΩ digunakan, yang tidak jelas buat sementara waktu.

Di atas ialah langkah berjaga-jaga asas semasa mengukur riak pensuisan. Jika probe osiloskop tidak terdedah secara langsung kepada titik output, ia harus diukur dengan garis berpintal atau kabel sepaksi 50Ω.

Apabila mengukur hingar frekuensi tinggi, jalur penuh osiloskop biasanya beratus-ratus paras mega hingga GHz. Yang lain adalah sama seperti di atas. Mungkin syarikat yang berbeza mempunyai kaedah ujian yang berbeza. Dalam analisis akhir, anda mesti mengetahui keputusan ujian anda.

Mengenai osiloskop:

Sesetengah osiloskop digital tidak dapat mengukur riak dengan betul kerana gangguan dan kedalaman storan. Pada masa ini, osiloskop perlu diganti. Kadang-kadang walaupun lebar jalur osiloskop simulasi lama hanya berpuluh-puluh mega, prestasinya lebih baik daripada osiloskop digital.

Perencatan riak kuasa pensuisan

Untuk menukar riak, secara teori dan sebenarnya wujud. Terdapat tiga cara untuk menyekat atau mengurangkannya:

1. Tingkatkan penapisan kearuhan dan kapasitor keluaran

Mengikut formula bekalan kuasa pensuisan, saiz turun naik semasa dan nilai kearuhan induktansi menjadi berkadar songsang, dan riak keluaran dan kapasitor keluaran adalah berkadar songsang. Oleh itu, meningkatkan kapasitor elektrik dan output boleh mengurangkan riak.

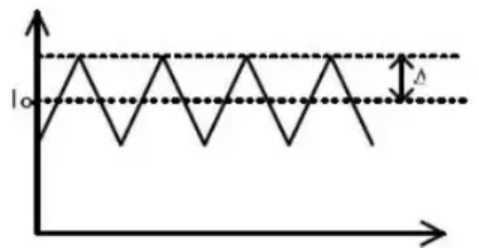

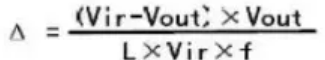

Gambar di atas ialah bentuk gelombang semasa dalam induktor bekalan kuasa pensuisan L. Arus riaknya △ i boleh dikira daripada formula berikut:

Dapat dilihat bahawa peningkatan nilai L atau peningkatan frekuensi pensuisan dapat mengurangkan turun naik semasa dalam induktansi.

Begitu juga, hubungan antara riak keluaran dan kapasitor keluaran: VRIPPLE = IMAX/(CO × F). Dapat dilihat bahawa peningkatan nilai kapasitor keluaran dapat mengurangkan riak.

Kaedah biasa adalah menggunakan kapasitor elektrolitik aluminium untuk kapasiti keluaran untuk mencapai tujuan kapasiti besar. Walau bagaimanapun, kapasitor elektrolitik tidak begitu berkesan dalam menyekat hingar frekuensi tinggi, dan ESR agak besar, jadi ia akan menyambungkan kapasitor seramik di sebelahnya untuk mengimbangi kekurangan kapasitor elektrolitik aluminium.

Pada masa yang sama, apabila bekalan kuasa berfungsi, VIN voltan terminal input tidak berubah, tetapi arus berubah dengan suis. Pada masa ini, bekalan kuasa input tidak menyediakan telaga semasa, biasanya berhampiran terminal input semasa (mengambil jenis wang sebagai contoh, adalah berhampiran Suis), dan menyambungkan kapasitansi untuk menyediakan arus.

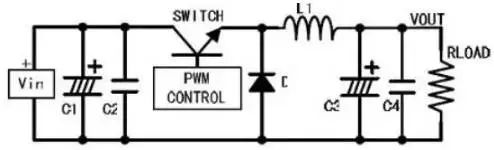

Selepas menggunakan langkah balas ini, bekalan kuasa suis Buck ditunjukkan dalam rajah di bawah:

Pendekatan di atas adalah terhad kepada mengurangkan riak. Kerana had volum, induktansi tidak akan menjadi sangat besar; kapasitor keluaran meningkat ke tahap tertentu, dan tidak ada kesan yang jelas untuk mengurangkan riak; peningkatan frekuensi pensuisan akan meningkatkan kehilangan suis. Jadi apabila syaratnya ketat, kaedah ini tidak begitu baik.

Untuk prinsip pensuisan bekalan kuasa, anda boleh merujuk kepada pelbagai jenis manual reka bentuk kuasa pensuisan.

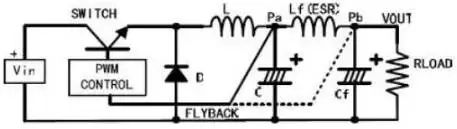

2. Penapisan dua peringkat adalah untuk menambah penapis LC peringkat pertama

Kesan perencatan penapis LC pada riak bunyi adalah agak jelas. Mengikut frekuensi riak yang hendak dikeluarkan, pilih kapasitor induktor yang sesuai untuk membentuk litar penapis. Secara amnya, ia boleh mengurangkan riak dengan baik. Dalam kes ini, anda perlu mempertimbangkan titik pensampelan voltan maklum balas. (Seperti yang ditunjukkan di bawah)

Titik pensampelan dipilih sebelum penapis LC (PA), dan voltan keluaran akan dikurangkan. Kerana mana-mana induktansi mempunyai rintangan DC, apabila terdapat keluaran semasa, akan terdapat kejatuhan voltan dalam kearuhan, mengakibatkan penurunan voltan keluaran bekalan kuasa. Dan penurunan voltan ini berubah dengan arus keluaran.

Titik pensampelan dipilih selepas penapis LC (PB), supaya voltan keluaran adalah voltan yang kita inginkan. Walau bagaimanapun, kearuhan dan kapasitor diperkenalkan di dalam sistem kuasa, yang boleh menyebabkan ketidakstabilan sistem.

3. Selepas keluaran bekalan kuasa pensuisan, sambungkan penapisan LDO

Ini adalah cara paling berkesan untuk mengurangkan riak dan bunyi. Voltan keluaran adalah malar dan tidak perlu menukar sistem maklum balas asal, tetapi ia juga merupakan yang paling kos efektif dan penggunaan kuasa tertinggi.

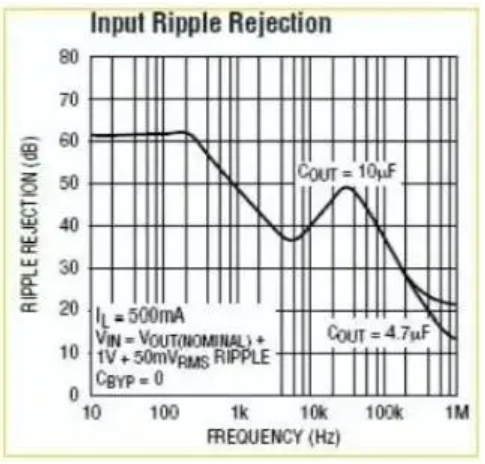

Mana-mana LDO mempunyai penunjuk: nisbah penindasan hingar. Ia ialah lengkung frekuensi-DB, seperti yang ditunjukkan dalam rajah di bawah ialah lengkung LT3024 LT3024.

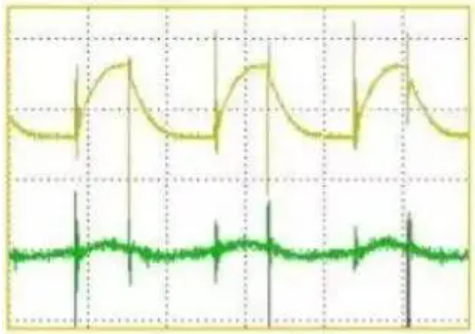

Selepas LDO, riak pensuisan biasanya di bawah 10mV. Angka berikut ialah perbandingan riak sebelum dan selepas LDO:

Berbanding dengan lengkung rajah di atas dan bentuk gelombang di sebelah kiri, dapat dilihat bahawa kesan perencatan LDO adalah sangat baik untuk riak pensuisan ratusan KHz. Tetapi dalam julat frekuensi tinggi, kesan LDO tidak begitu ideal.

Kurangkan riak. Pendawaian PCB bagi bekalan kuasa pensuisan juga kritikal. Untuk bunyi frekuensi tinggi, disebabkan oleh frekuensi frekuensi tinggi yang besar, walaupun penapisan pasca peringkat mempunyai kesan tertentu, kesannya tidak jelas. Terdapat kajian khas dalam hal ini. Pendekatan mudah ialah pada diod dan kapasitansi C atau RC, atau sambungkan kearuhan secara bersiri.

Rajah di atas ialah litar setara bagi diod sebenar. Apabila diod berkelajuan tinggi, parameter parasit mesti dipertimbangkan. Semasa pemulihan terbalik diod, kearuhan setara dan kemuatan setara menjadi pengayun RC, menghasilkan ayunan frekuensi tinggi. Untuk menyekat ayunan frekuensi tinggi ini, adalah perlu untuk menyambungkan kapasiti C atau rangkaian penampan RC pada kedua-dua hujung diod. Rintangan biasanya 10Ω-100 ω, dan kapasitansi ialah 4.7PF-2.2NF.

Kapasiti C atau RC pada diod C atau RC boleh ditentukan dengan ujian berulang. Jika ia tidak dipilih dengan betul, ia akan menyebabkan ayunan yang lebih teruk.

Masa siaran: Jul-08-2023