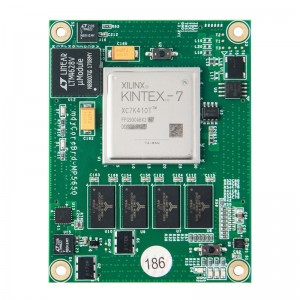

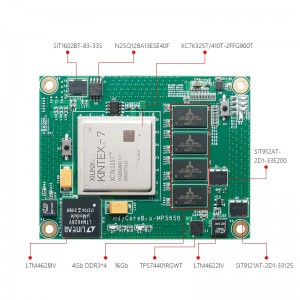

FPGA XILINX-K7 KINTEX7 XC7K325 410T gred industri

DDR3 SDRAMQ: 16GB DDR3, 4GB setiap keping, Bidaan Data Bit Data 16bit SPI Denyar: Satu keping 128MBITQSPIFLASH, yang boleh digunakan untuk fail konfigurasi FPGA dan storan data pengguna Tahap antara muka Bank FPGA: boleh laras 1.8V, 2.5V, 3.3V elektrik, jika anda hanya perlu menggantikan kedudukan magnet pada kedudukan elektrik yang sepadan, anda hanya perlu menggantikannya. pelarasan. Bekalan kuasa papan teras: Julat bekalan kuasa 5V-12V EEPROM; M24C02-WMN6TP adalah berdasarkan peranti bas I2C. Mengikuti kaedah permulaan papan teras protokol baris kedua: menyokong dua mod permulaan, iaitu JTAG, penyambung Flash QSPI. Port lanjutan, 120pin, Panasonic AXK5A2137yg MP5700 plat bawah antara muka SFP: 2 modul optik boleh mencapai komunikasi gentian optik berkelajuan tinggi, setinggi 6GB/s jam plat bawah: 1 200MHz jam rujukan disambungkan ke papan teras MRCC jam tiub kaki, 1 125MHz plat bahagian bawah tiub jam - kaki tiub GTX pin 4. port: simpan port sambungan 40 -shot jarak standard 2.54mm, yang digunakan untuk menyambung modul reka bentuk pelanggan sendiri. Jam papan Essence Core: terdapat berbilang sumber jam pada papan. Ini termasuk jam sistem 200MHz, jam GTX 125MHz dan jam EMCCLK 66MHz. Port JTAG: 10 jahitan port JTAG standard 2.54mm, untuk memuat turun dan menyahpepijat LED untuk program FPGA: sejumlah 6 lampu LED merah dalam papan teras, menunjukkan bekalan kuasa kad papan, 4 lampu penunjuk isyarat dan kaki tiub FPGA IO disambung terus Kunci: 4 kekunci. 4 kunci. Ia adalah butang set semula FPGA, kekunci Program_b dan dua kekunci pengguna.

FPGA Xilinx-K7 Kintex7 XC7K325 410T ialah model khusus FPGA (Field-Programmable Gate Array) yang dibangunkan oleh Xilinx. Berikut ialah beberapa butiran penting tentang FPGA:Siri ini: Kintex-7: FPGA siri Kintex-7 Xilinx direka untuk aplikasi berprestasi tinggi dan menawarkan keseimbangan yang baik antara prestasi, kuasa dan harga. Peranti: XC7K325: Ini merujuk kepada peranti khusus dalam siri Kintex-7. XC7K325 ialah salah satu daripada varian yang tersedia dalam siri ini, dan ia menawarkan spesifikasi tertentu, termasuk kapasiti sel logik, kepingan DSP dan kiraan I/O. Kapasiti Logik: XC7K325 mempunyai kapasiti sel logik sebanyak 325,000. Sel logik ialah blok binaan boleh atur cara dalam FPGA yang boleh dikonfigurasikan untuk melaksanakan litar dan fungsi digital. DSP Slices: Kepingan DSP ialah sumber perkakasan khusus dalam FPGA yang dioptimumkan untuk tugas pemprosesan isyarat digital. Bilangan tepat kepingan DSP dalam XC7K325 mungkin berbeza-beza bergantung pada varian tertentu. Kiraan I/O: "410T" dalam nombor model menunjukkan bahawa XC7K325 mempunyai sejumlah 410 pin I/O pengguna. Pin ini boleh digunakan untuk antara muka dengan peranti luaran atau litar digital lain. Ciri-ciri Lain: XC7K325 FPGA mungkin mempunyai ciri lain, seperti blok memori bersepadu (BRAM), transceiver berkelajuan tinggi untuk komunikasi data dan pelbagai pilihan konfigurasi. Penting untuk ambil perhatian bahawa FPGA seperti Xilinx-K7 Kintex7 XC7K325 yang membenarkan anda diprogramkan oleh litar dan peranti boleh logik tersuai. sel. Fleksibiliti ini menjadikannya sesuai untuk pelbagai aplikasi, termasuk pengkomputeran berprestasi tinggi, pemprosesan isyarat digital dan pecutan perkakasan.

Kategori produk

-

telefon

-

e-mel

-

Whatsapp

-

Skype

-

Skype

-

Skype